1 为什么要优化电源网络

在电源完整性方面,由于电源电压越来越低,而电流需求却越来越高,因此电源传输网络 (PDN)的设计变得非常重要,因为一个微小的电压噪声就会导致系统无法正常工作。另外, PDN 阻抗设计不足也会影响信号的完整性。在当前的电子产品中,为了确保良好的 PDN 设计,工程师们使用了大量去耦电容器来保证电源完整性,这些电容器在 PCB 和封装中占据了大量位置。 如何优化电容的位置和数量是工程师们经常面临的问题。

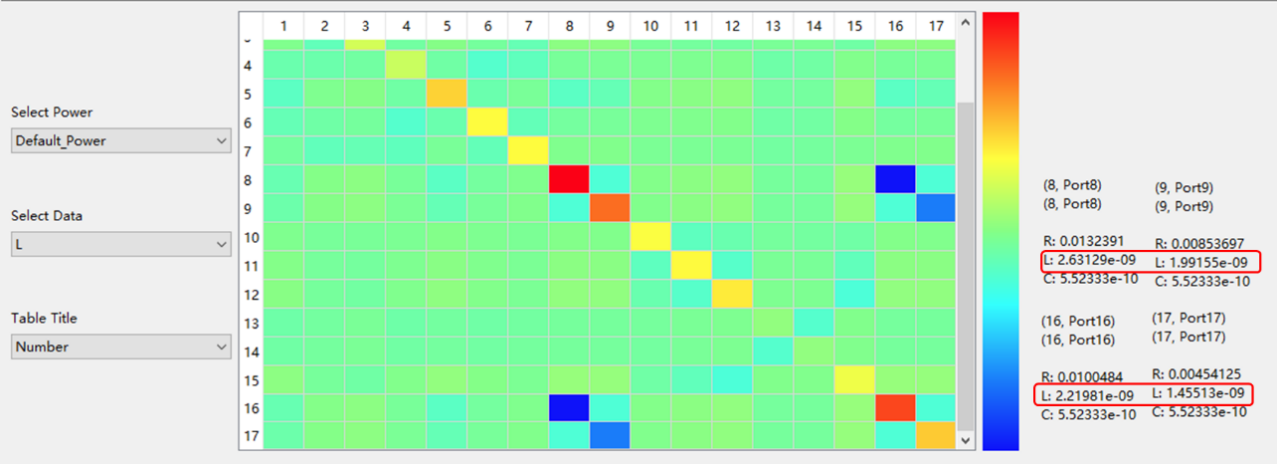

业界有很多关于去耦电容位置,容值以及数量优化相关的论文,但总体看来,论文的理论对 于工程的帮助很有限,因其经常需要多次的 3D Full wave 仿真进行迭代和优化,对仿真时间,以及资源需求较多,因此对于工程的帮助有限。各大 EDA 公司也有相应的一些去耦电容优化方案,这些 EDA 公司所出的方案经常是基于仿真一次所获得的 S 参数进行优化,这 样做的好处是优化速度快。但此等操作也有其弊端,类似陷入局部最优解,解的随机性等等, 但最重要的原因是,这些优化方式都是基于目标阻抗进行的。通常目标阻抗的定义为:

其中 Vdd是供电电压,Imax和 Imin分别是最大和最小工作电流,tolerance 是指器件在正常工作 时所能承受的最大电压的变化比例,比如说 5%。而且目标阻抗的定义实际上是有很多假设在里面的,这个目标阻抗并不能完美的描述时域噪声,类似 SSN, Voltage Droop 产生的机理, 它只是工程上一个很简单的估算公式,所用的假设是 PDN 是一个纯电阻,但事实上 PDN 网络设计中最重要的挑战是电源分配网络所产生的电感,其主要是由电流回路路径而引起的,电感的阻抗会随频率升高而升高,过高的阻抗将会引起过大的电源噪声,并且电感 可以与电源网络的寄生电容一起产生谐振,因此我们经常需要加入大量的电容来对阻抗曲线进行优化。

2 使用 S2SPICE 来优化 PDN 的电感

2.1 使用 S2SPICE 来抽取 PDN 的具有物理意义的等效电路

如果我们可以确定电流回路路径,那么对于 PDN 的设计来说,就可以对其电流回路路径进行优化,通过降低电流回路路径的距离来降低电感。遗憾的是,由于 PCB 设计的复杂性,工 程师很难通过版图来确定电流回路路径,往往需要大量的仿真来对电流回路路径进行确认。

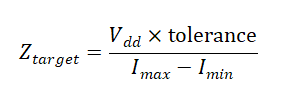

现在业界有一款特色的小工具,S2SPICE,其提出了一种对于 PDN 优化的新思路,能够基于 PDN 的 S 参数生成其对应的具有物理意义的等效电路,这个提取的等效电路不仅可以用作全通路 PDN 时域瞬态仿真,而且提供了评估和优化 PDN 阻抗的一个新思路和新工具。

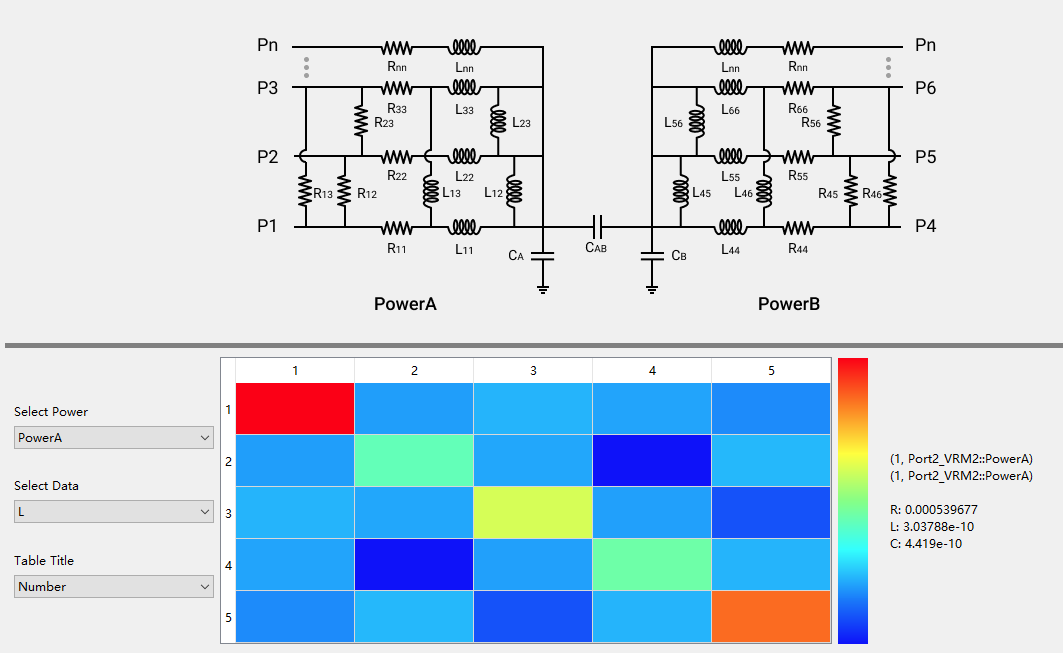

该软件可以从 PDN 的 S 参数中提取出每个端口处的电阻以及电感。 从刚刚的分析中,我们得知 PDN 的寄生电感对于 PDN 优化的重要性。因此,该软件还集成 了对于 R map 以及 L map 的显示,可以轻松知道每个端口处的电感的大小以及其影响,以 及最大最小的 R, L。对于 IC 负载的电源端口来说,其相应的电感决定了 PCB PDN 对这个负载所能提供的最小阻抗的极限值,也就是决定了 PCB 层级下的 PDN 网络的有效性;对于去 耦电容端口来说,其对应的电感决定了这个去耦电容阻抗的大小,也就是决定了去耦电容的有效性。

图1 L map

图2 R map

2.2 优化 PDN 的电感

端口处电感的大小是 PDN 优化的一个重要指标

1:SI/PI 工程师可以通过该结果来对封装的 ball map 或者 IC 的 bump map 进行重新布局, 对电源和地 pin 脚的数量和位置排布进行优化,使较为重要的电源可以有较低的电感。

2:工程师可以通过端口的电感大小来决定在该端口附近所添加的电容类型,数量,大小等; 也可以对电容处的过孔放置以及数量进行优化,越小的端口处的电感可以使电容更具有效 性,因为放置电容所带来的寄生电感 ESL 会和端口处的电感进行并联,因此减少端口处的电感及可以减少电容所带来的寄生电感。

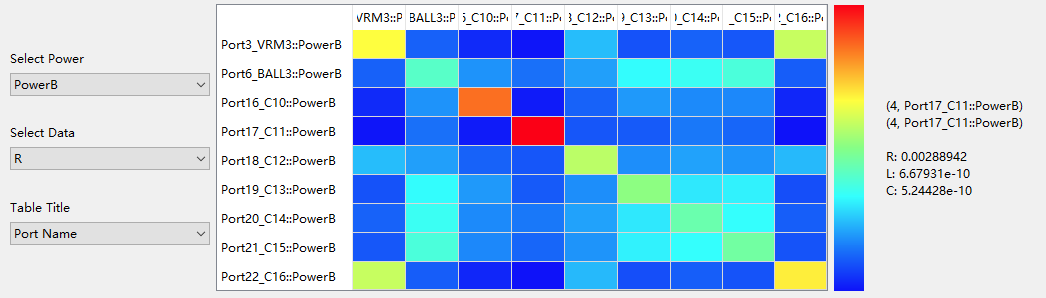

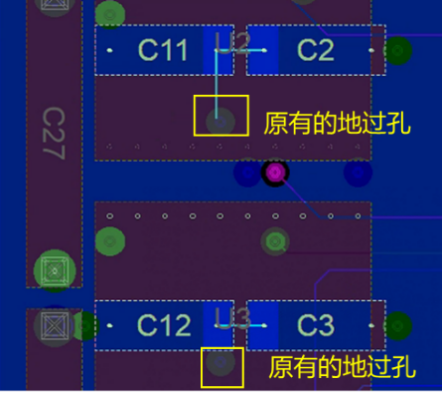

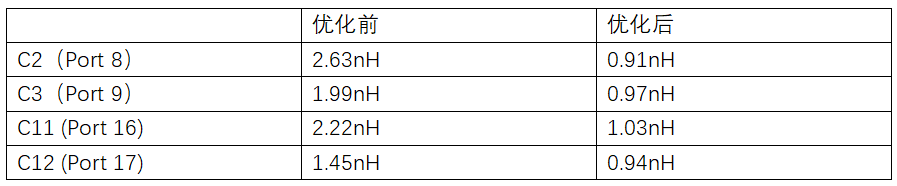

为此,我们准备了一个简单的电容过孔优化案例作为示例。案例如图 4-1,原有的版图设计 将电容的地过孔放置于电容负极下方,距离电容 pad 较远,并且两个电容共用同一个地过孔,还用了很细的线进行连接,这种的连接方式并不友好,我们对原有电容处的地过孔进行了优化,在 C2 和 C11 电容负极 pad 处各自加入了两个地过孔,在 C3 和 C12 电容负极 pad 处各自加入了一个地过孔。

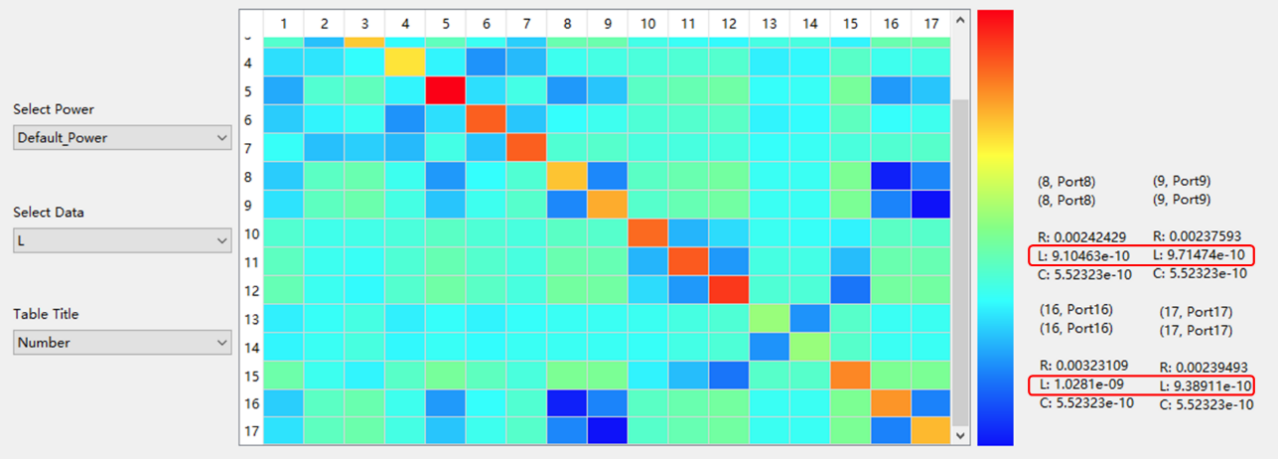

先对案例原始设计进行仿真,一共17个端口,其中电容C2, C3, C11, C12分别对应第8,9,16,17 个端口。仿真结果如由图 5 所示,端口 8,9,16,17 处的电感分别为 2.631nH , 1.991nH, 2.22nH, 1.45nH。

图3 仿真结果 – 优化前各个端口处的电感图

图3 -1 原有的电源网络版图设计

图3 -2 优化后的电源网络版图设计

对优化后的设计进行再次仿真,结果如图 6 所示,可以看到红色框标注 port8(C2),port9 (C3),port16 (C11) 以及 port17 (C12)处的电感比图 4 中的电感小了很多。

图4 仿真结果 – 优化后各个端口处的电感图

对比优化前后的结果,可以看到比较差的几个端口电感均有明显改善。

此案例只是为了说明这种分析和优化的方法,实际的工程案例中,问题会更加复杂,要考虑的因素也更多,但是其原理基本相通 ,S2Spice 可以帮助工程师快速定位问题,从而解决问 题。

3 使用 S2SPICE 所提取的物理等效电路的限制

3.1 PCB 和封装级的阻抗参数分析

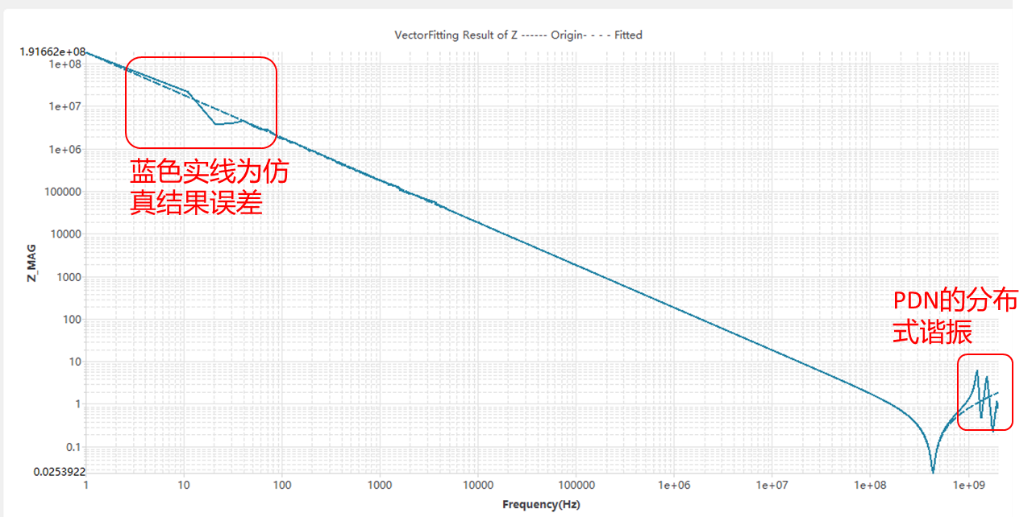

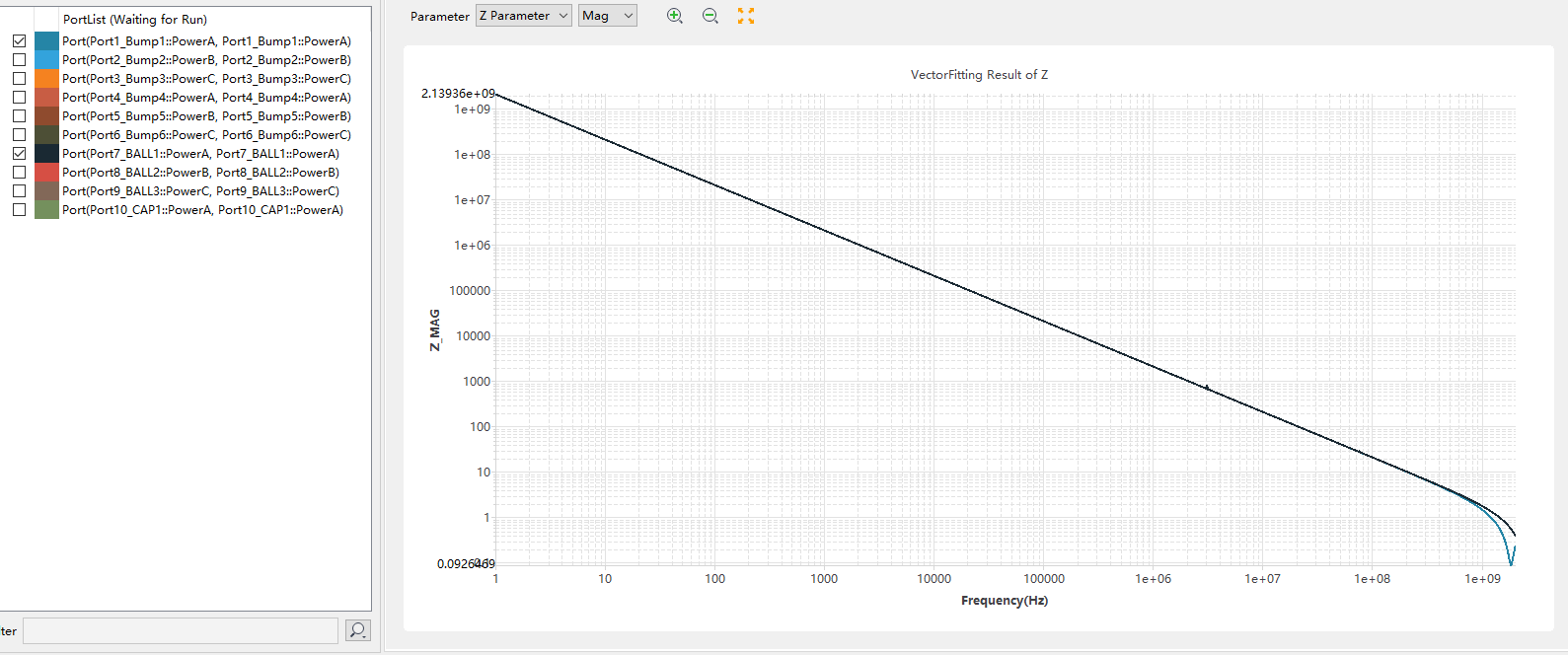

S2SPICE 所提取的具有物理意义的等效电路对 PDN 网络的分布式谐振无法进行处理, 如图 7-1 所示。也就是该等效电路对于不考虑高频谐振的情况较为友好。而且大部分的 板级 PCB,并不是需要考虑特别高的频率,因为比较高的频率的 PDN,它的噪声是由封装 和芯片上的电容来决定的,那么到了 PCB 板级这边,那我们的频率并不需要那么高;再一 个,即使对于封装级,因封装的尺寸也一般较小,其 PDN 结构(不含电容)的阻抗曲线一 般在 2GHz 以内只有一个谐振点甚至一个谐振点都没有,因此该谐振点较高,也可以用 S2SPICE 所提取的具有物理意义的等效电路来很好的描述,如图 7-2 所示。

图5-1:一阶RLC等效电路阻抗曲线

图5-2:封装级阻抗曲线

抽取具有物理意义的等效电路只是 S2SPICE 中的一个功能,如果用户对高频的分布式谐振信息也很关注,S2SPICE 也提供了传统的矢量拟合的方法,也能处理大规模,大数量端口的拟合。

3.2 全通路时域瞬态仿真验证

PDN 仿真除了频域阻抗的仿真,最重要的一环是全通路的时域瞬态仿真。在工程实践中,一般不直接使用 S 参数来做时域的瞬态仿真,因为通常会遇到不收敛的问题,使用 S2SPICE 提取的具有物理意义的等效电路可以有效的解决不收敛的情况。但是,S 参数 转换成 Spice 模型的过程中,市场上的软件很容易产生精度丢失。基于以上介绍,S2Spice 在算法上做了很多创新,完美的解决了这个问题。

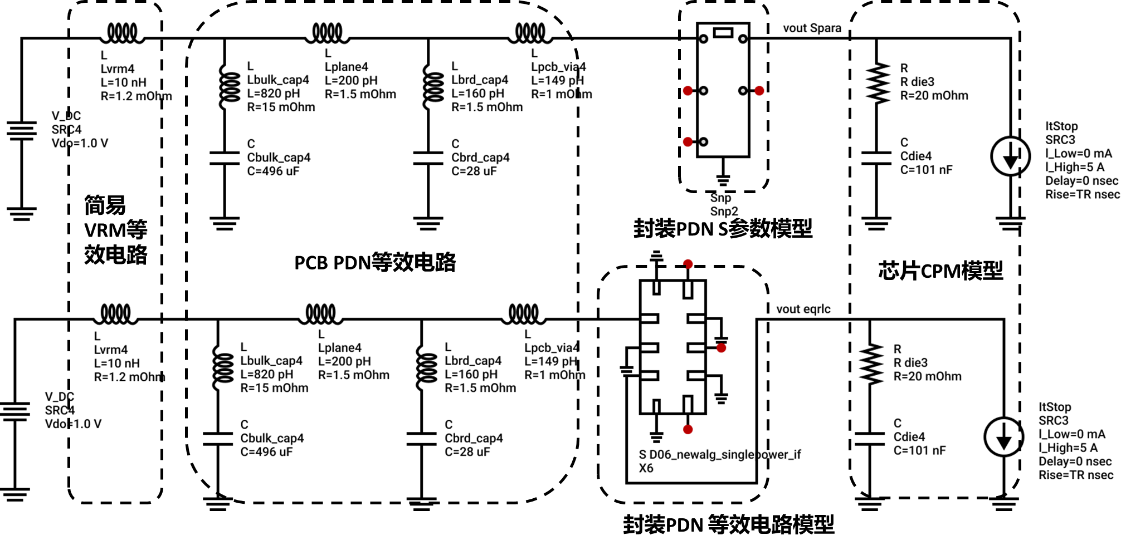

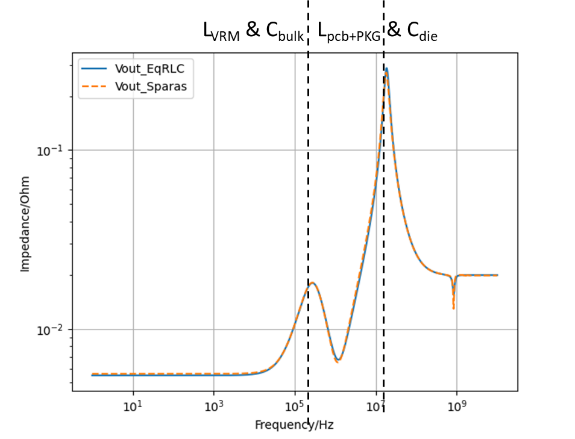

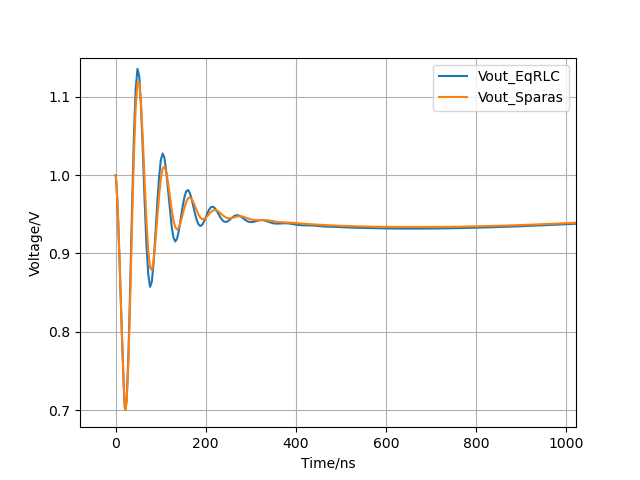

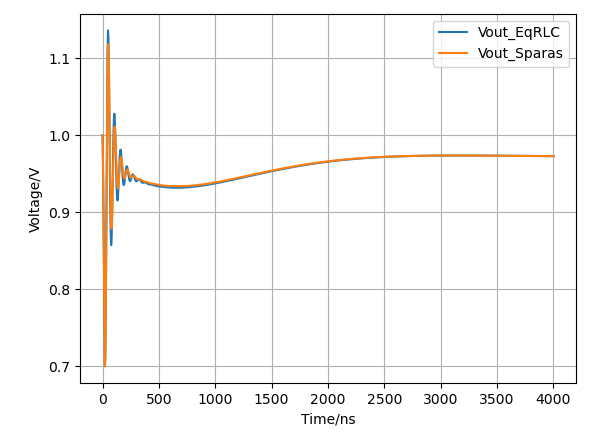

接下来,我们用一个实际案例来对比一下使用 S2Spice 所提取出来的等效电路和直接使用频域 S 参数来进行时域仿真的结果,验证其精度和准确度。

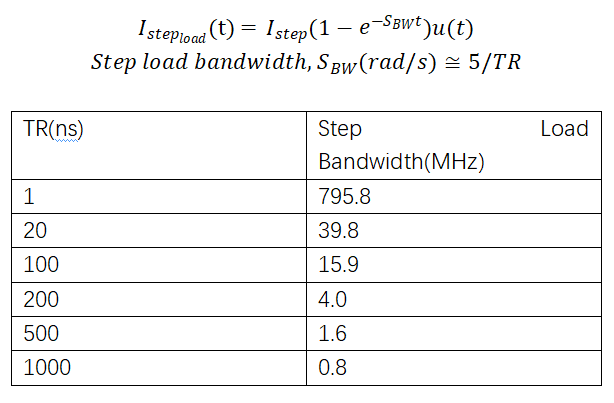

因为我们是一个封装级别的 S 参数,为保证结果的通用性,特意加入了板级等效电路, 芯片级的 CPM 模型,我们选取的上升沿 TR = 20ns,如图 8 所示。根据下列的公式和表格,其大致对应的 step load bandwidth 为 39.8MHz 来进行 Voltage Droop 分析。

图6:Voltage droop仿真设置验证,阻抗曲线比对

图7:First Droop 和Second Droop 对比

该对比结果证明了 S2Spice 产生的等效电路的准确性,不论是从频域或者时域出发,均证明了其结果的有效性。

3.3 S2SPICE 其他功能

S2SPICE 不仅可以进行模型转换,也集成了 S 参数常用的处理功能,可以支持数据的前处理, 数据对比,以及数据后处理,直接查看结果,无需导出 S 参数用其他工具查看阻抗曲线对比。

➢ 集成了多种数据前处理模式:包含删选频段,端口删减排序,重采样,重归一化等

➢ 集成了数据的后处理模式,可以直接看到 S,Y,Z 并对其做端口删减排序,短路检查,导 出文件等操作,一站式服务

➢ 还集成了专门开发了可以抽取具体物理意义等效模型的算法以及对特殊部分进行精度 强化的算法

4 更多信息

对 S2SPICE 工具感兴趣的,可以在下面网页获取进一步信息

https://www.detooltech.com/product.html#sonic-s2spice

5 参考文献

L. Y. Foo, "Power Delivery Network Step Load Response and 1st Droop Formulation," 2019 Electrical Design of Advanced Packaging and Systems (EDAPS), Kaohsiung, Taiwan, 2019, pp. 1-6, doi: 10.1109/EDAPS47854.2019.9011667